그것이 알고 싶다, ‘세계 최초 10나노급 8기가비트 D램 양산’의 의미

2016/04/05

‘나노’는 사람 눈으로 확인할 수 없는 단위다. 반도체 산업에선 바로 이 나노 단위로 치열한 경쟁을 벌인다. 초미세 공정을 통해 차세대 초고속∙초절전 기술을 먼저 확보하는 게 중요하기 때문이다. 이 과정을 통해 선도 업체는 더욱 높은 생산성을 추구한다. 지속적으로 이익을 창출하며 성장 가능한 체질로 끊임없이 변화해가는 것이다. 그 결과, 소비자는 한층 개선된 내구성과 사용 편의성을 갖춘 고성능∙저전력 제품을 사용할 수 있게 된다.

삼성전자는 오늘(5일) “2월부터 10나노급 8Gb(기가비트) DDR4 D램(이하 ‘10나노급 D램’)을 양산하고 있다”고 밝혔다<관련 보도자료는 여기 참조>. 지난 2014년 2월 세계 최초로 20나노 4Gb DDR3 D램(이하 ‘20나노 D램’)을 양산한 데 이어 2년여 만의 일이다. 최첨단 기술 개발에 사활을 걸며 극심한 경쟁 구도를 형성하고 있는 반도체 업계에서 삼성전자가 또 한 번 새로운 역사를 쓴 것이다. 초미세공정 기술 개발 끝에 성공시킨 10나노급 D램 양산, 얼마나 대단한 일이고 어떤 기술이 사용된 걸까?

D램 공정 미세화, 왜 어려운 기술이라고들 할까?

반도체는 크게 두 종류로 나뉜다. 컴퓨터∙스마트폰 등에서 데이터 연산∙처리 기능을 맡고 있는 ‘시스템 반도체’가 하나, 데이터 저장용으로 쓰이는 ‘메모리 반도체’가 다른 하나다. D램은 메모리 반도체 중에서도 아주 빠른 속도로 작동하는 중앙처리장치(CPU)나 그래픽처리장치(GPU)가 요구하는 데이터를 임시로 저장, 처리하는 역할을 담당한다.

하나의 D램 칩은 수억 개의 셀(cell)로 구성된다. 각각의 셀은 데이터를 저장하는 캐패시터(capacitor)와 데이터를 제어하는 트랜지스터(transistor)로 구성된다. 삼성전자가 이번에 양산한다고 한 10나노급 D램은 8Gb. 80억 개 이상의 셀이 들어갔다는 얘기다.

D램과 같은 집적회로(Integrated Circuit, IC) 칩은 얇은 실리콘 원판(일명 ‘웨이퍼’) 위에 전자 회로를 새긴 후 이를 다시 작은 조각으로 절단해 만든다. 이때 웨이퍼 위에 더 미세한 설계와 공정이 적용될수록 더 많은 IC 칩이 생산될 수 있다.

삼성전자가 양산하고 있는 10나노급 D램에선 하나의 웨이퍼에서 이전 제품(20나노 D램)보다 30% 이상 많은 1000개 이상의 칩이 생산된다.

▲1나노는 10억 분의 1단위다. 20나노로 만든 칩을 100개로 가정했을 때 공정이 10나노급으로 미세해지면 130여 개의 칩을 생산할 수 있다. 생산성이 30% 이상 향상되는 셈이다

▲1나노는 10억 분의 1단위다. 20나노로 만든 칩을 100개로 가정했을 때 공정이 10나노급으로 미세해지면 130여 개의 칩을 생산할 수 있다. 생산성이 30% 이상 향상되는 셈이다

10나노급 D램 양산 가능케 한 독자적 핵심 기술 3

이번 ‘10나노급 D램 양산’ 성공 배경엔 삼성전자가 독자적으로 개발한 세 가지 혁신적 기술이 숨어 있다. 사중 포토 노광 기술(Quadruple Patterning Technique, 이하 'QPT')과 초균일 유전막 형성 기술, 그리고 초고집적 설계 기술이 그것이다.

#1. 한 번에 더 작게, 더 많이… 사중 포토 노광 기술

반도체 제조 공정의 관건은 ‘손톱만 한 칩에 나노 단위 회로를 설계하는’ 기술에 있다. ‘20나노’니 ‘10나노급’이니 하는 용어는 셀을 작동시키는 비트 라인(bit line)과 워드 라인(word line)에 적용된 공정의 평균 값을 일컫는다. 다시 말해 웨이퍼 표면에서 반짝이는 메탈 공정 패턴이 아니라 그 아래 부분에 형성된 초미세 회로 공정 패턴을 가리킨다.

10나노급 D램 공정엔 ‘포토(photo) 설비’가 사용된다. 사람 육안으로 보이지 않는, 얇고 강력한 레이저 빛으로 초미세 회로를 그리는 설비다. ‘포토’란 명칭은 웨이퍼 위에 전자 회로를 (사진 찍어내듯) 그린다고 해서 붙여졌다. QPT는 단 한 번의 포토 공정으로 초미세 패턴을 네 배 많이 만들어낼 수 있는 기술. 주로 낸드플래시 양산에 적용돼왔다. 삼성전자는 미세공정의 한계를 극복하기 위해 업계 최초로 이 QPT를 D램 공정에 구현했다.

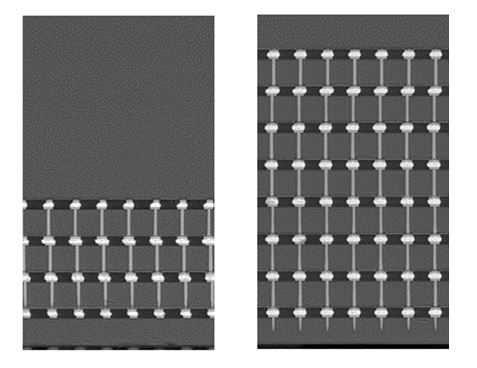

▲10나노급 D램 양산에 적용된 QPT의 구동 원리. 한 차례 포토 공정으로 네 배 많은 초미세 패턴을 만들어낼 수 있는 기술이다

▲10나노급 D램 양산에 적용된 QPT의 구동 원리. 한 차례 포토 공정으로 네 배 많은 초미세 패턴을 만들어낼 수 있는 기술이다

#2. 작고 얇으며 단단하게… 초균일 유전막 형성 기술

하나의 D램을 구성하는 수십 억 개 셀 중 하나라도 문제가 생기면 기기는 제대로 작동하지 않는다. 따라서 고성능∙저전력 칩을 만들 땐 해당 셀이 오랫동안 완벽하게 작동할 수 있도록 안정성까지 고려해야 한다. 이를 위해선 각각의 캐패시터를 ‘얇고 길며 단단하게’ 만들 필요가 있다. 그 열쇠를 쥐고 있는 게 바로 초균일 유전막 형성 기술이다.

캐패시터는 전자(데이터)를 임시로 담아두는 역할을 한다. 주변 회로는 캐패시터에 담긴 전자를 통해 전하 유무를 각각 ‘0’과 ‘1’로 판단, 디지털 신호를 구분한다. 캐패시터에 충분한 양의 전자가 담길수록 디지털 신호를 더 빨리 판단할 수 있다. 공정을 미세화하면서 충분한 전자를 담아두려면 캐패시터를 더 얇고 길게 만들어야 하는 구조다.

캐패시터를 만들 땐 안에 담기는 전하가 너무 빠르게 새지 않도록, 그리고 바로 옆 캐패시터 전하의 영향을 받지 않도록 얇고 단단한 유전막을 씌워야 한다(한 번 더 강조하지만 캐패시터와 캐패시터 사이 간격은 수십 나노에 불과하다). 초균일 유전막 형성 기술의 핵심은 바로 이 유전막을 균일하게 유지하는 데 있다. 제품 양산력과 경쟁력을 끌어올리는, 반도체 제조 공정의 핵심 기술이다.

▲삼성전자는 독자적으로 개발한 물질을 캐패시터 안팎에 코팅, 유전막을 옹스트롬 단위의 초박형 원자 물질로 균일하게 만드는 데 성공했다

▲삼성전자는 독자적으로 개발한 물질을 캐패시터 안팎에 코팅, 유전막을 옹스트롬 단위의 초박형 원자 물질로 균일하게 만드는 데 성공했다

공정이 미세화될수록 캐패시터 크기는 줄어든다. 작아진 캐패시터에서는 상단 부분에 박막 물질이 두텁게 뭉쳐지는 과흡착 현상이 생길 경우, 안정적 셀 특성 확보가 어려워진다.

삼성전자의 기술력이 또 한 번 입증된 건 바로 이 지점이다. 업계 최초로 10나노급 D램에 초균일 유전막 형성 기술을 적용, 이 같은 문제를 극복한 것. 삼성전자는 독자적으로 개발한 물질을 캐패시터 내∙외부에 코팅함으로써 유전막을 (나노의 1/10인) 옹스트롬 단위의 초박형 원자 물질로 균일하게 만드는 데 성공했다. 이로써 10나노급 D램은 종전 제품보다 한층 향상된 성능을 갖추면서도 안정적으로 작동할 수 있게 됐다.

#3. 빠르지만 전력 소비는 적게… 초고집적 설계 기술

일반적으로 반도체의 동작 속도는 소비 전력에 비례한다. 즉 속도가 빨라질수록 전력 소비는 늘어나는 구조다. 하지만 10나노급 D램은 전작에 비해 속도가 빨라진 대신 소비 전력은 오히려 줄었다. 비결이 뭘까?

10나노급 D램은 속도를 높여 데이터를 더 빨리 제어, 처리한 후 대기(idle) 상태로 전환되도록 설계됐다. (회로 설계 수준에 따라 차이가 있지만) 대기 상태에선 활동(active) 상태에 비해 훨씬 적은 전력을 소비한다. 10나노급 D램이 ‘데이터 처리 속도 개선’과 ‘소비 전력 절감’ 두 마리 토끼를 잡을 수 있는 비결이다.

▲20나노 D램에서 2.4Gbps였던 동작 속도는 10나노급 D램으로 넘어오며 3.2Gbps로 향상됐다(PC∙서버 이용 기준)

▲20나노 D램에서 2.4Gbps였던 동작 속도는 10나노급 D램으로 넘어오며 3.2Gbps로 향상됐다(PC∙서버 이용 기준)

실제로 PC나 서버 시스템 환경에서 10나노급 D램의 작동 속도(3.2Gbps)는 전작이었던 20나노 D램(2.4Gbps)에 비해 크게 향상됐다. 또한 작동 상태에 따라 소비 전력 역시 10~20% 절감됐다. 삼성전자는 PC∙서버용 제품에 이어 올해 중 용량과 성능을 동시에 개선한 10나노급 모바일 D램도 양산, 초고해상도 스마트폰 시장을 지속적으로 선점해나갈 계획이다.

데이터 처리 속도 향상에만 초점을 맞출 경우, 소비 전력을 늘리는 쪽으로 기술을 개발하면 된다. 하지만 전력 소비의 영향을 크게 받는 모바일 기기용 D램에선 풀(full) HD급은 물론, 4K UHD급 초고해상도 영상 데이터의 안정적 처리 능력이 필수다. 모바일 D램을 만들 때 ‘속도를 높이는 동시에 소비 전력량(배터리 사용량)을 절감하는’ 기술이 반드시 필요한 건 그 때문이다.

결국 △초미세 패턴을 한꺼번에 그려내는 사중 포토 노광 기술 △개별 캐패시터를 얇고 단단하게 만드는 초균일 유전막 형성 기술 △이 둘을 최적의 상태로 조합, ‘초고속∙초절전 구현’의 성과로 이어지게 하는 초고집적 설계 기술 등 3대 핵심 기술의 동시 구현이 10나노급 D램 양산의 비결인 셈이다.

‘프리미엄 D램 시장 선도’ 삼성의 역사는 계속된다

오늘 양산 사실이 발표된 삼성전자 10나노급 D램은 이전 모델인 20나노 D램과 비교했을 때 생산성과 속도가 각각 30% 이상 향상됐고 소비 전력 절감 효과도 약 20%에 이른다. 삼성전자는 이번 성과에 만족하지 않고 앞으로도 PC와 서버는 물론, 모바일 기기에 이르기까지 전 부문에서 ‘프리미엄 D램’ 시장을 지속적으로 선도해나갈 것이다.