三星投產GAA架構3奈米製程晶片

優化的3奈米製程較5奈米製程降低45%功耗、提升23%效能並縮減16%面積

▲三星晶圓代工事業部與半導體研發中心負責人比出3的手勢,慶祝邁向GAA架構3奈米製程的嶄新里程碑。

全球先進半導體技術領導品牌三星電子宣布,已啟用環繞式閘極(GAA)架構的3奈米製程製造晶片。

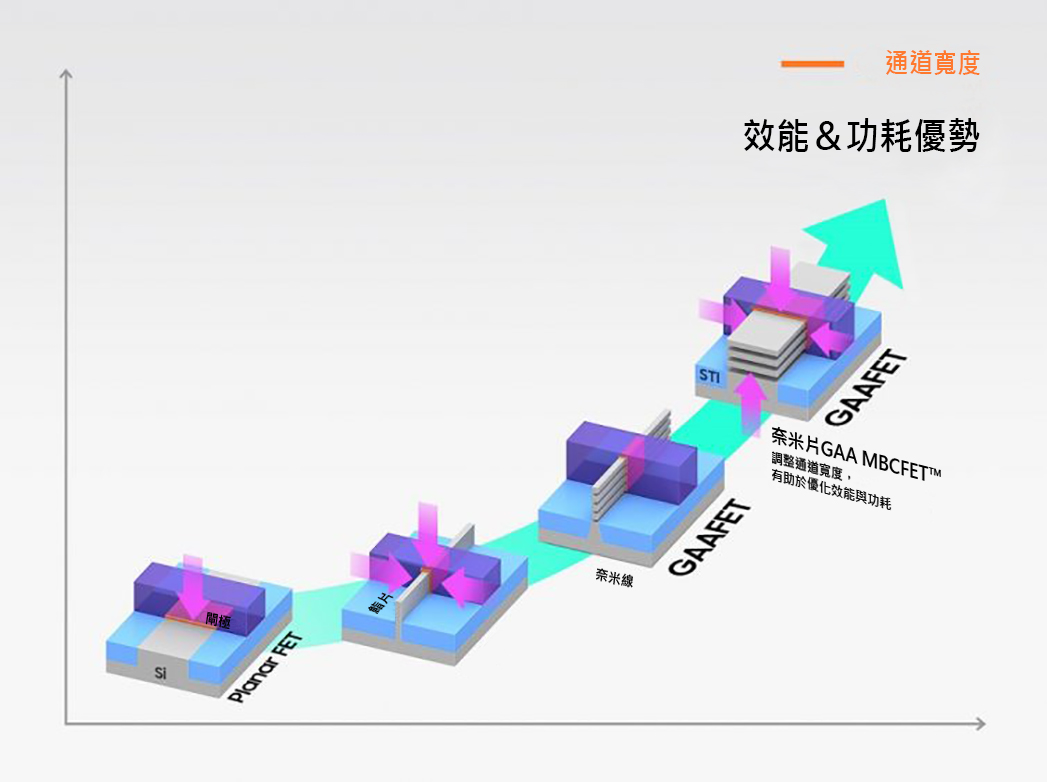

三星首次採用多橋通道場效電晶體FET(MBCFET™)的GAA技術生產晶片,突破「鰭式場效電晶體」(FinFET)架構的性能限制,並藉由減少供應電壓層級優化功率效率,同時透過增加驅動電流能力提升效能。

三星將具有奈米片電晶體架構的半導體晶片,首次應用於高效能、低功耗的運算領域,並計畫拓展至行動處理器。

三星電子總裁暨晶圓代工事業部負責人Siyoung Choi博士表示:「三星不斷導入業界第一技術,例如高介電常數金屬閘極(High-K Metal Gate)、FinFET以及EUV等,展現飛躍性成長,在製造應用層面持續坐穩領導地位。三星冀望以領先全球的MBCFET™架構3奈米製程,鞏固技術霸主之位。展望未來,我們將延續強勁的創新動能,積極開發具競爭優勢的技術,並建立有助於加速技術成熟的流程。」

▲(左起)三星電子副總裁Michael Jeong、執行副總裁Ja-Hum Ku,以及三星晶圓代工事業部副總裁Sang Bom Kang三人手持3奈米晶圓,於三星華城園區生產線合影。

藉由優化設計技術,實現最大化PPA

三星的專有技術採用通道較寬的奈米片,相較於通道較窄的奈米線GAA技術架構,能實現更高效能與更佳的能源效率。在3奈米GAA技術助陣下,三星得以調節奈米片的通道寬度,優化功耗以及效能表現,滿足客戶的多元需求。

此外,GAA設計的靈活性,具有提升功耗、效能、面積(PPA)的優勢,對於設計技術整合優化(DTCO)十分有利(註一)。相較於5奈米製程,第一代3奈米製程能降低45%功耗、提升23%效能、縮減16%面積;第二代3奈製程則可降低50%功耗、提升30%效能,並縮減35%面積。

攜手SAFE™ 夥伴提供3奈米設計基礎架構與服務

隨著技術節點的持續微縮,與晶片效能提升的需求成長,為驗證功能更多、尺寸縮減的複雜產品,IC設計人員面臨著處理龐大數據的挑戰。為滿足上述需求,三星致力提供更穩定的設計環境,以減少設計、驗證和簽核流程所需時間,同時提升產品的可靠性。

得益於三星與Ansys、Cadence、Siemens和Synopsys等先進製程晶圓代工生態圈(SAFE™)夥伴的縝密佈局,三星自2021年第三季起,便開始提供經驗證的設計架構,協助客戶在更短時間內完善產品設計。

來自SAFE™ 合作夥伴的證言

- Ansys,Ansys電子、半導體和光學業務部副總裁暨總經理John Lee

「Ansys攜手三星持續為最先進的設計打造致能技術,如今以GAA技術實現3奈米製程,Ansys多物理場模擬平台的簽核準確度,便是我們與位居業界領先地位的三星晶圓代工事業部,維持長期合作關係的一大例證。Ansys維持一貫不變的承諾,竭力為雙方共同的頂級客戶,提供最佳的設計體驗。」

- Cadence,Cadence客製化IC及PCB事業群資深副總裁暨總經理Tom Beckley

「三星邁向GAA架構3奈米製程的里程碑,我們對此表達恭賀之意。Cadence與三星晶圓代工事業部密切合作,使客戶透過我們的數位解決方案-從元件庫特性到全數位流程實施與簽核,於該節點實現最佳功耗、效能與面積,達成最大化的生產效率,而背後最大的驅動力皆來自於Cadence Cerebrus AI技術。奠基於自家的客製解決方案,我們攜手三星啟用並驗證完整的AMS流程,藉由自動佈線來提高電路設計和模擬的生產效率。我們熱切期待雙方延續合作關係,促成更多的成功設計定案。」

- Siemens EDA,西門子數位化工業軟體IC-EDA執行副總裁Joe Sawicki

「Siemens EDA很高興與三星合作,並確保從最初的開發階段起,我們現有的軟體平台能在三星最新的3奈米製程節點運作。雙方藉由SAFE™ 計劃建立的長期夥伴關係,使西門子領先業界的EDA工具通過3奈米認證,為雙方的共同客戶創造巨大價值。」

- Synopsys,新思科技矽晶實現事業部總經理暨公司幕僚Shankar Krishnamoorthy

「基於與三星晶圓代工事業部長期建立的策略夥伴關係,我們以解決方案支援三星的先進製程,協助共同客戶大幅縮短設計週期。Synopsys將持續擴大對三星GAA架構3奈米製程的支援廣度,我們的Digital Design、Analog Design和IP產品,助力客戶為關鍵的高效能運算應用,提供差異化SoC。」

註一:有關設計技術整合優化(DTCO)的更多資訊,請參閱以下連結:

Find the optimal for the best. Part 1

Find the optimal for the best. Part 2

關於消費者服務相關詢問,請洽三星客服專線 : 0800-32-9999

任何媒體需求及詢問,請聯繫 tw.newsroom@samsung.com.